SEMICONDUCTOR ICs RELIABILITY

-

Smart Power

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

-

SoC

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

-

MEMS

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

-

Memories

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

-

Smart Power

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

-

SoC

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

-

MEMS

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

-

Memories

- Des. Validation

- Qualification

- Smart BI

- TDBI

- Process Monitoring

- System Level Test

ELECTRONIC MODULES RELIABILITY

-

Safety & ADAS

-

Power Train

-

Body Control & Comfort

-

Infotainment

-

Avionics

-

Navy

-

Space

-

Terrestrial

Smart digital solutions for your productivity close to you

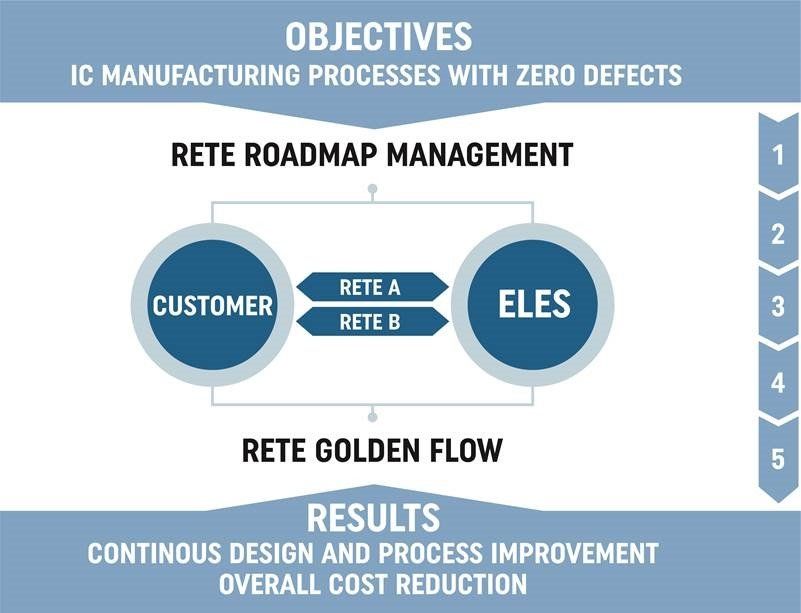

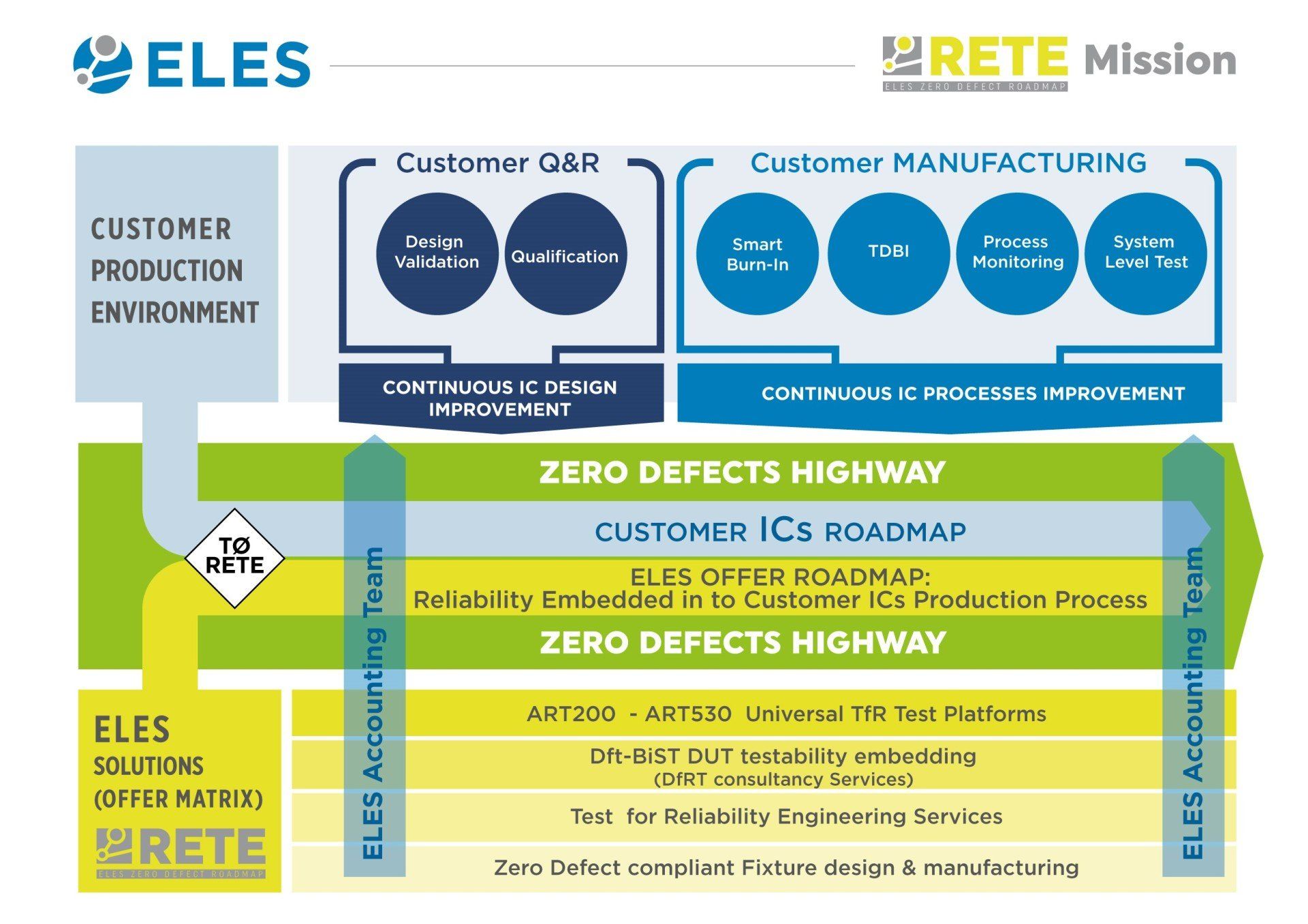

RETE business model

- Design: Design For Reliability

In order to ensure the highest reliability, semiconductor devices should be designed for reliability. As with DFM (Design for Manufacturing) and DFT (Design for Testing), additional silicon structures are embedded during the IC Design to address reliability aspects of the devices.

- Qualification: TFR for Q&R

The DUT (Device Under Test) is put and simultaneously tested into a stable climatic and electronic environment, where an adequate combination of both thermal and electronic signals (“Adaptive Stress Matrix”) stimulates a wide range of failures modes. Advanced algorithms detect potential failures before they actually fail by picking up signatures of latent defects (e.g. an electric value which starts drifting). Detailed Reliability data from Engineering validation & qualification lots are analyzed to optimize design and process, with the least number of design iterations.

- Manufacturing: TFR for Production

Instead of testing with ATE before and after Burn-In, the test is done during Burn In (TDBI). Reliability data are gathered and analyzed for process improvement. Based on results, the number of hours of TDBI are progressively reduced and replaced by a Process Monitoring with samples taken from production lots.

ELES TEST PLATFORMS

TEST SYSTEM CONFIGURATIONS

ELES SERVICES

- Design for Reliability Test (DfRT) Consultancy: Consulting activity for the designer carried out in the concept phase of the device and aimed at optimizing the testability and observability of the device blocks and functions to improve the devices quality and reliability.

- Test for Reliability (TfR) Consultancy: Consultancy activity carried on during the definition of the reliability test, oriented to the definition of the key parameters to be monitored, of the data to be collected, of the flow to be implemented.

- Application Development Support (ADS): Analysis of customer’s device specifications and trial requirements which allow ELES to design fit for purpose Fixtures, Test programs for the specific applications. During this phase ELES will partner with the customers Device designers, Q&R and Test engineers.

- SIGNAL INTEGRITY post layout Simulation: Signal Integrity Post Layout Simulation based on ART tester + Interface board + Fixture + DUT Model simulation (IBIS or SPICE models). Data Analysis, Circuit and Layout Parameters Tuning to achieve optimal SI performances of the Application on the specific DUT.

- Power INTEGRITY post layout Simulation: Power Integrity Post layout simulation based on ART Tester + Interface board + Fixture layouts to evaluate the quality of power supply levels and possible fine tuning of the fixture layout.

- Test for Reliability (TfR) configuration: Definition for each single test of the sequence of stress and tests and data logging

- Test Program Development: Test Program code development according to Device Test list Specification and Test for Reliability flow

- Test Pattern Generation: Generation of the stimuli - in Eles proprietary format - starting from Device Datasheet and/or Test Pattern Specification

- Device Diagnostic Descr & Decode: Device diagnostic registers interpretation and analog measurement description for the use of Real Time SW Interpreter

- Application Integration: Verification of the first board on test bench based on the trial specification. Followed by its integration with the DUT and test program, and the validation of the whole package at ambient temperature. An application report is then generated and shared with the client for approval.

- DUT Functional characterization: Characterization of the devices ambient functional behavior based upon agreed electrical and functional parameters not including temperature. The results of the test will be inserted in to the Application Integration report

- DUT Thermal characterization: Characterization of the devices thermic behavior in a temp range with the objective of defining the trial setup. The results of the test will be inserted in to the Application Integration report

- Data Analysis For Reliability Improvement: Analysis of the data collected during the trial execution with the aim of finding Root Causes of the defects.

- Socket Functional Verification: ELES will verify the chosen socket and device package to ensure the functional integration against final application. This excludes verification of the socket against the data sheet. The results of the test will be inserted in to the Application Integration report.

Call

Call