半导体 集成电路的可靠性

电子模块可靠性

贴身的生产力智能数字解决方案

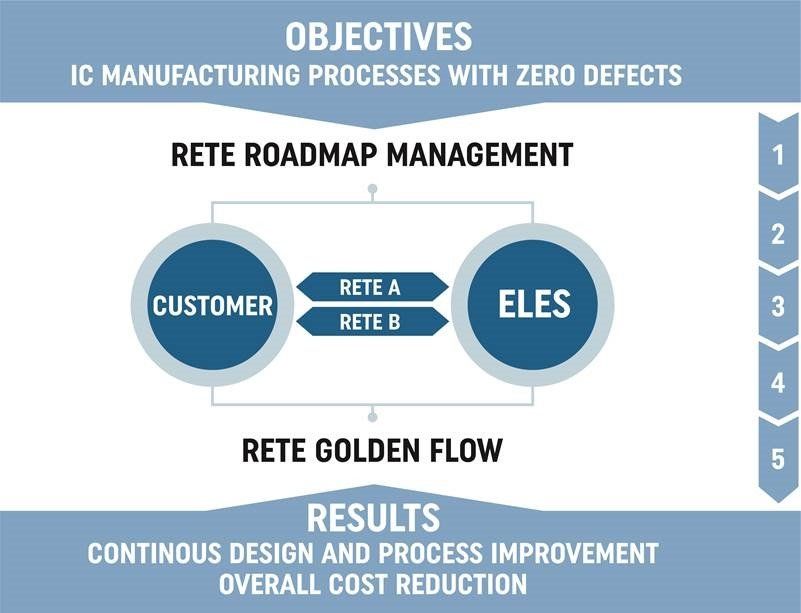

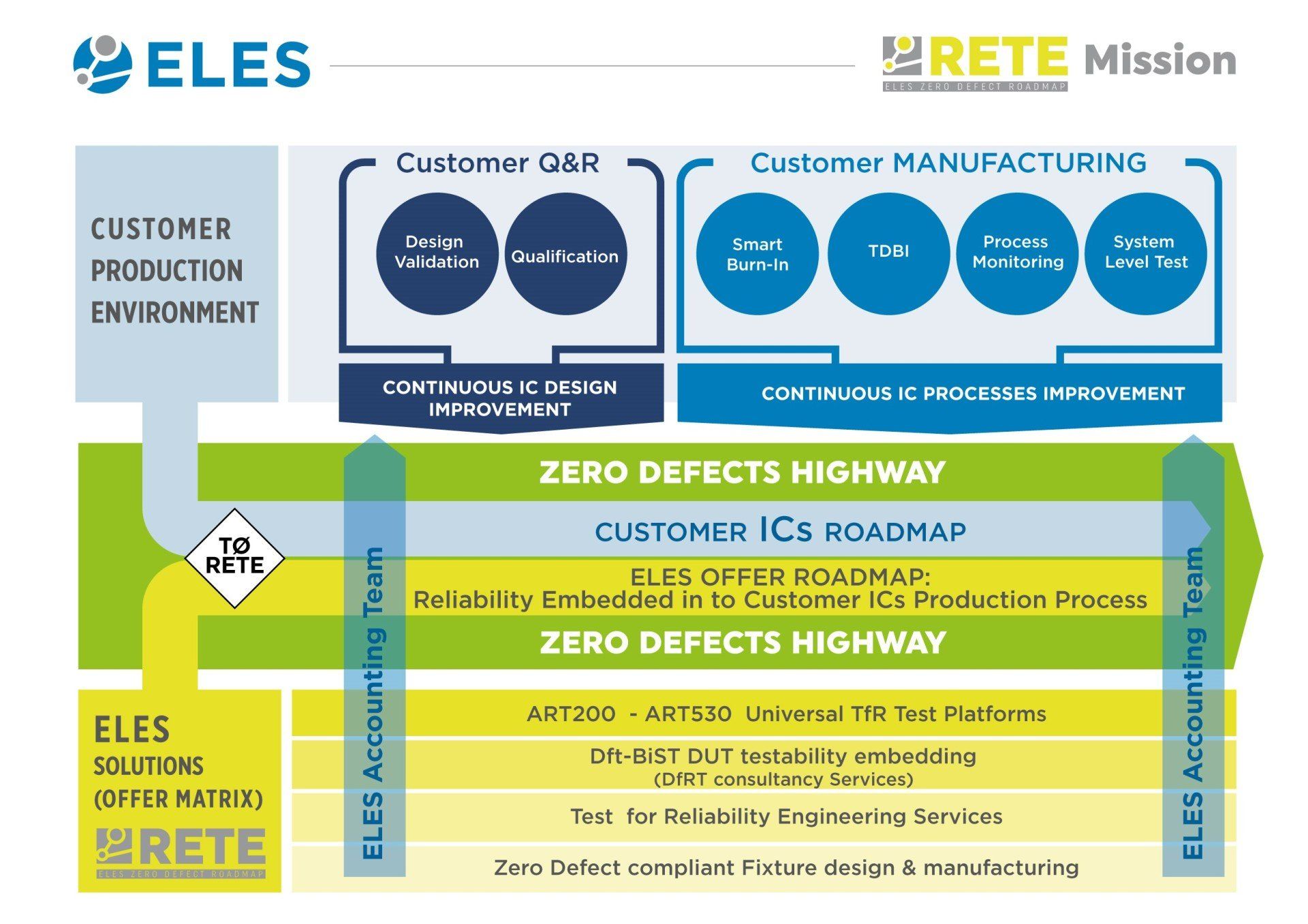

RETE 商业模式

ELES 测试平台

测试系统的设置

ELES 服务内容

- 可靠性测试的设计(DfRT)咨询:在设备的概念设计阶段就对设计人员提供咨询活动,旨在优化设备模块和功能的可测试性和可观察性,以提高设备质量和可靠性。

- 可靠性测试(TfR)咨询: 在可靠性测试的定义期间就进行的咨询活动,参与被监控的关键参数的定义,被收集的数据的定义,以及实施的流程。

- 应用程序开发支持(ADS): 通过分析客户的设备规格和试验要求,ELES能够设计专用的夹具以及特定的测试程序。在此阶段,ELES将与客户的设备设计师,Q&R和测试工程师紧密合作。

- 信号完整性(SIGNAL INTEGRITY)后期布局模拟: 信号完整性的后期布局模拟基于ART测试仪 + 接口板 + 夹具 + DUT模组模拟(IBIS或SPICE模组)的结构。数据分析,电路和布局参数调整以在特定的被检测设备上实现应用的最佳的信号完整性。

- 电源完整性(Power INTEGRITY)后期布局模拟:电源完整性后期布局模拟基于ART测试仪 + 接口板 + 夹具的结构,用于评估供电级别的质量以及夹具布局的更合理的调整。

- 可靠性测试(TfR)配置: 定义压力测试和数据记录序列的每个单独测试

- 测试程序开发: 随着设备测试的进行和可靠性检测的深入进行的测试程序代码开发

- 测试激励(Test Pattern Generation):生成激励 - 转换为ELES可识别格式 - 从设备数据表和/或测试模式规范开始

- 设备诊断描述和解码: 设备诊断寄存器的解释和模拟测量的描述,用于使用实时SW解释器

- 应用集成: 根据试验规范来验证测试台上的第一块母板。接着进行被测设备DUT和测试程序的集成,并在环境温度下验证整个封装。然后生成应用程序报告并与发予客户以验证规范。

- DUT功能特性: 基于商定的电气和功能参数(不包括温度)表征设备的环境功能行为测试。测试结果将写入到应用程序集成报告中。

- DUT热特性: 在温度范围内表征设备的热行为记录与分析,定义被测设备的热行为。测试结果将写入到应用程序集成报告中。

- 可靠性改进的数据分析: 分析试验期间收集的数据,找出缺陷的根本原因。

- 测试插座功能性验证: ELES将验证选定的测试插座和器件封装,以确保与最终应用程序的功能集成的完整性。这不包括测试插座对数据表的验证。测试结果将写入到应用程序集成报告中。

联系电话

联系电话